# B.Sc. PHYSICS – I YEAR DJK1B : BASIC ELECTRONICS SYLLABUS

# **Unit I : Diodes**

P-n junction diode – characteristics – Regulation with zener diodes – Bridge rectifier – clipping and clamping circuits with diodes.

# **Unit II : Transistors and Amplifiers**

Transistors – Transistor action – three modes of connection – biasing – load line and Q –point – voltage divider bias – stabilization – CE amplifier.

# **Unit III : Oscillators**

Principles of negative voltage feed back in amplifiers – gain – advantages – principle of negative current feedback – Oscillation – Bark Hausen criterion for oscillation – colpitt's oscillator

# **Unit IV : Field Effect Transistor**

Principle , features and characteristics of FET – JFET and MOSFET – their characteristics – enhancement and depletion type

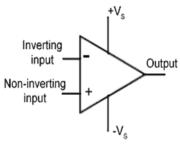

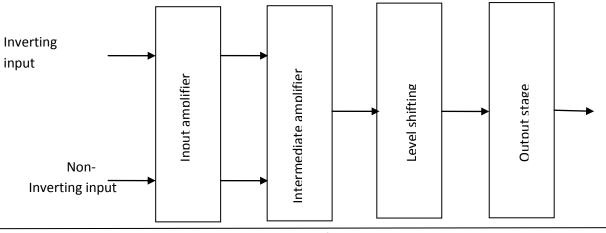

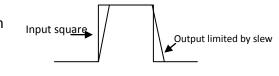

# **Unit V : Operational Amplifier**

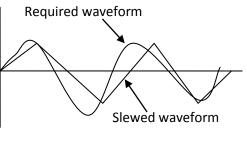

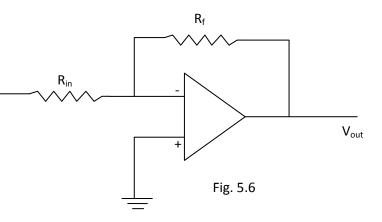

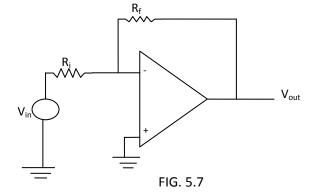

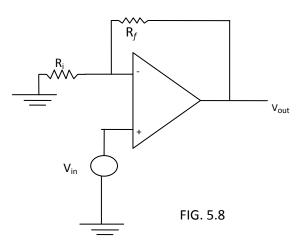

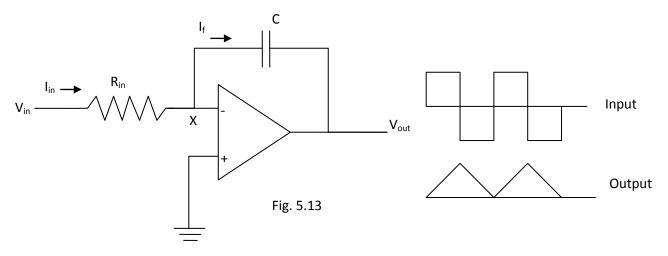

Characteristics – slew rate – inverting and non-inverting amplifier – adder – sub tractor – integrator – differentiator

# Books for study and reference:

- 1. Fundamentals of Electronics B. Ghosh

- 2. Principles of Electronics V.K. Mehtha

### **UNIT I : DIODES**

*P-N junction diode – characteristics – Regulation with zener diodes – Bridge rectifier – clipping and clamping circuits with diodes.*

#### 1.1 Semiconductors

Semiconductor is a solid substance that has a conductivity between that of an insulator and that of metal due to the addition of an impurity. Devices made of semiconductors, are the essential components of most electronic circuits. Semiconductors include antimony, arsenic, boron, carbon, germanium, selenium, silicon, sulfur, and tellurium. Silicon is the best-known of these, forming the basis of most integrated circuits . Common semiconductor compounds include gallium arsenide, indium antimonide, and the oxides of most metals. Of these, gallium arsenide (Ga-As) is widely used in low-noise, high-gain, weak-signal amplifying devices.

**Types of Semiconductors:** Semiconductors are mainly classified into two categories: They are (a) Intrinsic Semiconductors and (b) Extrinsic Semiconductors

#### (a) Intrinsic Semiconductor

An electron is called a negative charge carrier and a hole ( absence of an electron) is called a positive charge carrier. An intrinsic semiconductor material is chemically very pure and possesses poor conductivity. It has equal numbers of negative charge carriers and positive charge carriers. A silicon crystal is different from an insulator because at any temperature above absolute zero, there is a finite probability that an electron in the lattice will be knocked loose from its position, leaving behind an electron deficiency or a *hole*.

If a voltage is applied, then both the electron and the hole can contribute to a small current flow. The conductivity of a semiconductor can be modelled in terms of the band theory of solids. The band model of a semiconductor suggests that at ordinary temperatures there is a finite probability that electrons can reach the conduction band and contribute to electrical conduction.

# (b) Extrinsic Semiconductor

An extrinsic semiconductor is an improved intrinsic semiconductor with a small amount of impurities added by a process, known as *doping*. This alters the electrical properties of the semiconductor and improves its conductivity. Introducing impurities into the semiconductor materials can control their conductivity. Doping process produces two groups of semiconductors: the majority negative charge conductor (n-type) and the positive charge conductor (p-type). Semiconductors are available as either elements or compounds. Silicon and Germanium are the most common elemental semiconductors.

# 1.2 Doping of Semiconductors

Pentavalent impurities (5-valence electrons) produce n-type semiconductors by contributing extra electrons. Trivalent impurities (3-valence electrons) produce p-type semiconductors by producing a hole or electron deficiency.

# (a) n-Type Semiconductor

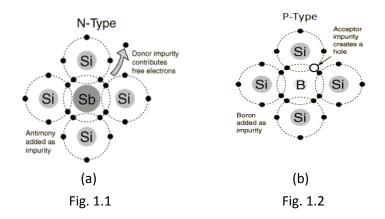

The addition of pentavalent impurities [fig. 1.1] such as antimony, arsenic or phosphorous contributes free electrons, greatly increasing the conductivity of the intrinsic semiconductor. In this type, the current conduction is mainly due to the electrons, and the holes are the minority carriers. This forms n-type semiconductor.

# (b) p-Type Semiconductor

The addition of trivalent impurities [fig. 1.2] such as boron, aluminum or gallium to an intrinsic semiconductor creates deficiencies of valence electrons, called *holes*. In this type, the current conduction is mainly due to the holes, and the electrons are the minority carriers. This forms p-type semiconductor.

# 1.3 p-n Junction Diode

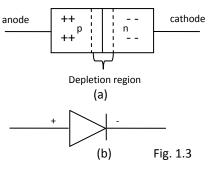

When n-doped and p-doped semiconductor are fused together to form a junction, electrons migrate from the n-side into the p-side and holes migrate from the p-side into the n-side. Following this transfer, the diffused electrons come into contact with holes on the p-

side and are eliminated by recombination. Likewise for the diffused holes on the n-side. The net result is a region with no mobile carriers. This region is called *depletion region*. The symbols used for a p-n junction diode are shown in the fig. 1.3

### 1.4 Energy Band Diagram of p-n junction diode

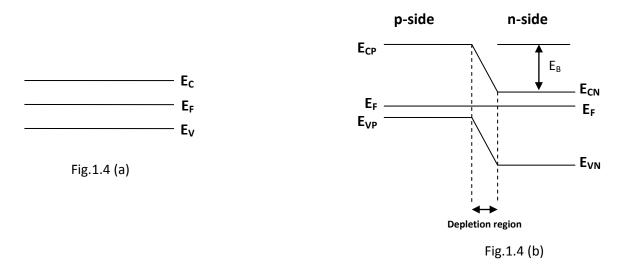

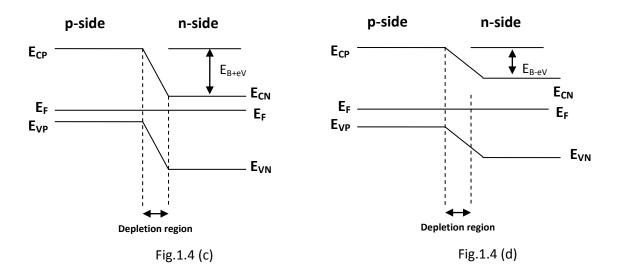

The *Fermi energy* is defined as the energy difference between the highest and lowest occupied single-particle states in a quantum system of non-interacting fermions at absolute zero temperature. For n-type semiconductor, the Fermi level  $E_F$  lies near the conduction band edge  $E_C$  but for p - type semiconductor,  $E_F$  lies near the valance band edge  $E_V$ . Now,

when a p-n junction is built, the Fermi energy  $E_F$  attains a constant value [fig. 1.4(b)]. In this situation the p-side conduction band edge. Similarly n–side valance band edge will be at higher level than  $E_{cn}$ , n-sides conduction band edge of p - side. This energy difference is known as barrier energy. The barrier energy is  $E_B = E_{cp} - E_{cn} = E_{vp} - E_{vn}$  If we apply reverse bias

voltage V, across the junction, then the barrier energy increases by an amount of eV (fig. 1.4(c)) and if is forward bias is applied, the barrier energy decreases by eV [fig. 1.4(d)]

### 1.5 Forward and reverse biased p-n Junction

Biasing means application of voltage. To make a p-n junction to conduct, electrons should move from the n-type region to the p-type region and holes moving in the reverse direction. To overcome the potential barrier across the junction, a battery is connected to the two ends of the p-n junction diode. The battery can be connected to the p-n junction in two ways:

Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli.

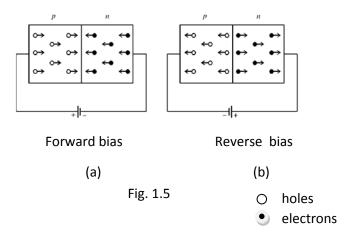

Positive terminal of the battery connected to the p-side and negative terminal of the battery connected to the n-side. This is called *forward bias* [fig. 1.5(a)]. If positive terminal of the battery is connected to the n-side and negative terminal of the battery connected to the p-side, then it is called *reverse bias* [fig. 1.5(b)].

When a junction is forward biased and the bias exceeds barrier potential, holes are compelled to move towards the junction and cross from the p-region to the n-region. Similarly, electrons cross the junction into the p-region. This sets in forward current in the diode. The current increases with voltage and is of the order of a few milli-amperes. Under the forward bias condition, the junction offers low resistance to flow of current. The value of junction resistance, called forward resistance, is in the range  $10\Omega$  to  $30\Omega$ .

When the p-n junction is reverse biased, holes in the p-region and electrons in the n-region move away from the junction. A small current flows even now. This small current caused by minority carriers is called reverse saturation current or leakage current. Thus a p-n junction offers a low resistance when forward biased, and high resistance when reverse biased. This property of p-n junction is used for ac to dc rectification. When the reverse bias voltage is of the order of a few hundred volt, the current through the p-n junction increases rapidly and damages it due to excessive power dissipation. The voltage at which a diode breaks down is termed as *breakdown voltage*. When a reverse bias is applied, a large electric field is established across the junction. This field will:

(i) accelerate the available minority carriers, which in turn, collide with the atoms of the semiconductor material and eject more electrons through energy transfer (*avalanche effect*)

(ii) break covalent bonds by exerting large force on electrons bound by the bonds. This results in creation of additional electron-hole pairs in the junction region .

# 1.6 Characteristics study of a junction diode

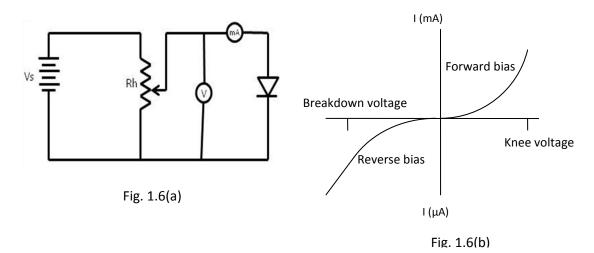

# (i) Forward bias characteristics

Circuit Connections are made as shown in the fig. 1.6(a) using a p-n junction diode. Initially the voltage applied to the diode is varied in steps of 0.1 V by using the rheostat ( $R_h$ ). Once the current starts increasing, the voltage is varied from 1V to 12V in steps of 1V and the

corresponding forward biased voltage readings ( $V_f$ ) in the voltmeter (V) and the corresponding forward biased current ( $I_f$ ) in the milli ammeter (mA) are noted and the readings are tabulated as shown in the table. A suitable graph is drawn by taking  $V_f$  on x-axis and  $I_f$  on y-axis. This gives the forward bias characteristic curve.

### (ii) Reverse bias characteristics

To study the reverse bias characteristics of the diode, a circuit connection is made as shown in the fig. 1.6(a), but with the polarities of the diode are changed and the milliammeter is replaced with a micro ammeter. The procedure is repeated as in forward bias mode and the readings are tabulated. A suitable graph is drawn giving the reverse bias characteristic curve for the given p-n diode.

| S.No. | Forward / Reverse bias in |  | Forward bias/Reverse bias |  |

|-------|---------------------------|--|---------------------------|--|

|       | volts                     |  | current in mA/ $\mu$ A    |  |

|       |                           |  |                           |  |

|       |                           |  |                           |  |

|       |                           |  |                           |  |

#### TABLE 1

The characteristic curve for a p-n junction diode is shown in the fig.1.6 (b). In the forward bias mode, the current increases very slowly in the beginning and then increases rapidly.

The point at which the current starts to increase rapidly is known as knee voltage. In the reverse mode, the current increases with voltage and reaches a point where it remains almost constant with further increase in voltage. This voltage is called *break down voltage* of the given diode.

#### 1.7 Zener Diode

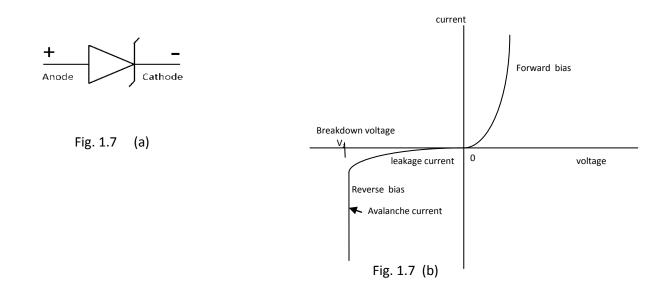

A Zener Diode is a special kind of diode which permits current to flow in the forward direction as normal, but will also allow it to flow in the reverse direction when the voltage is above a certain value, the breakdown voltage known as the Zener voltage. The symbol used is shown in the fig. 1.7(a)

The zener voltage of a standard diode is high, but if a reverse current above that value is allowed to pass through it, the diode is permanently damaged. Zener diodes are designed so that, when a reverse current above the zener voltage passes through a zener diode, there is a controlled breakdown which does not damage the diode. The voltage drop across the zener diode is equal to the zener voltage of that diode. The fig. 1.7 (b) shows a current vs. voltage graph. With a zener diode connected in the forward direction, it behaves exactly the same as a standard diode. In the reverse direction however there is a very small *leakage current* between 0V and the zener break down voltage. Then, when the voltage reaches the breakdown voltage (Vz), suddenly current flows freely through it.

# **Uses of Zener Diodes**

- 1) They are used as reference voltages for circuits.

- 2) Zener diodes are used to regulate the voltage in electric circuits.

- 3) They are used as over voltage protector.

# 1.8 Zener Diode as Voltage Regulator

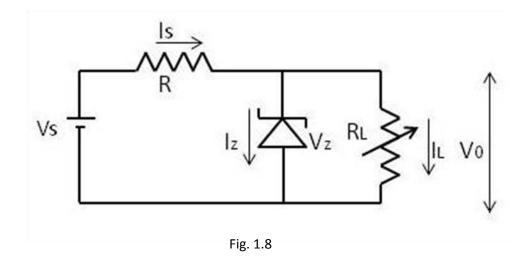

A voltage regulator circuit can be designed using a zener diode to maintain a constant DC output voltage across the load in spite of variations in the input voltage or changes in the load current. The zener diode is always operated in its reverse biased condition.

In the fig. (1.8), by using Kirchoff's current law, we can write

$$I_s = I_z + I_L$$

If  $I_L$  decreases due to change in load resistance,  $I_z$  increases since  $I_s$  is constant. Even then V<sub>z</sub> remains constant. When  $I_L$  increases,  $I_z$  decreases to keep  $I_s$  constant. Thus V<sub>z</sub> is always constant. That is the voltage across the load is always constant.

Also, when Vs exceeds the rated voltage of the device, the breakdown voltage is reached at which avalanche breakdown occurs in the semiconductor depletion layer of the zener diode and a current starts to flow through the diode, thus maintaining a constant current flow

through the load. The current now flowing through the zener diode increases dramatically to the maximum circuit value, which is usually limited by a series resistor and once achieved this reverse saturation current remains constant over a wide range of applied voltages. The voltage point at which the voltage across the zener diode becomes stable is called the *zener voltage*. For zener diodes this voltage can range from less than one volt to hundreds of volts.

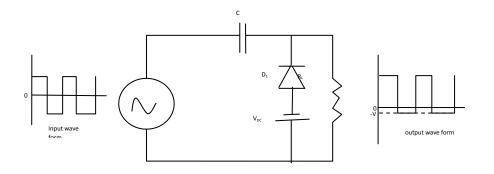

#### 1.9 Bridge Rectifier

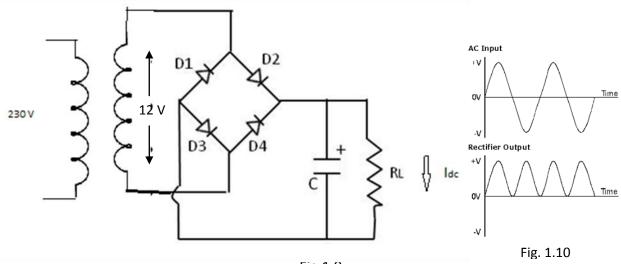

#### Construction

A Bridge rectifier is an alternating current (AC) to direct current (DC) converter. The bridge rectifier circuit diagram is shown in the fig. 1.9. It consists of a step down transformer which converts the AC mains 230V to 12V AC supply. Next stage uses four diodes in the form of a bridge as shown. Since the output after the diode bridge rectifiers is of pulsating, a filter circuit is used. The filter consists of one or more capacitors across the load.

Fig.1.9

#### Working

During the positive half cycle of secondary voltage, diodes D2 and D3 are forward biased and diodes D1 and D4 are reverse biased. Now the current flows through D2, Load ( $R_L$ ) and D3. During the negative half cycle of the secondary voltage, diodes D1 and D4 are forward biased and rectifier diodes D2 and D3 are reverse biased. Now the current flows

through D4, Load and D1. In both the cycles, load current flows in the same direction. Hence we get a pulsating DC voltage as shown in fig 1.10. So a filter circuit is added to reduce the pulsation in the output wave form.

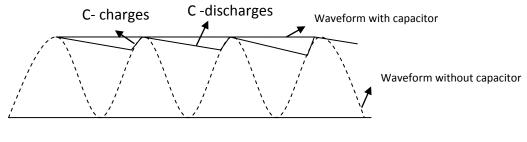

#### 1.10 Capacitor filter

A capacitor is shunted across the output of a rectifier. This capacitor is also shunted with a load resistor. This addition of a capacitor at the output converts the pulsating DC voltage to fixed DC voltage. Upto a time period (say t=1s) input voltage is increasing, so the capacitor charges up to a peak value of the input. After t=1s, the input starts to decrease, then the voltage across the capacitor reverse biases the diodes D2 and D4 and therefore these diodes will not conduct. Now capacitor discharges through the load and hence voltage across the capacitor decreases. When the peak voltage exceeds the capacitor voltage, diodes D2 or D4 are forward biased and as a result capacitor again charges to the peak value. This process continues. Hence we get almost smooth DC voltage as shown in fig. (1.11).

Fig. 1.11

#### 1.11 Ripple factor

Small unwanted residual periodic variation of the direct current (DC) output of a power supply which has been derived from an alternating current (AC) source is called *ripple*. Ripple factor ( $\gamma$ ) is defined as the ratio of the root mean square (rms) value of the ripple voltage to the absolute value of the DC component of the output voltage. It is expressed as a percentage.

#### **1.12** Effects of ripple

Ripple is undesirable in many electronic applications for a variety of reasons. They are,

- The ripple frequency and its harmonics are within the audio band and will therefore be audible on equipment such as radio receivers, equipment for playing recordings and professional studio equipment.

- 2) The ripple frequency is within television video bandwidth. Analogue TV receivers will exhibit a pattern of moving wavy lines if too much ripple is present.

- 3) The presence of ripple can reduce the resolution of electronic test and measurement instruments. In an oscilloscope, it will manifest itself as a visible pattern on screen.

- 4) Within digital circuits, it reduces the threshold, at which logic circuits give incorrect outputs and data is corrupted.

- 5) High-amplitude ripple currents shorten the life of electrolytic capacitors.

# 1.13 Peak Inverse Voltage (PIV)

Peak Inverse Voltage or Peak Reverse Voltage (PRV) refers to the maximum voltage a diode or other device can withstand in the reverse-biased direction before it breaksdown. In a rectifier circuit, during negative half cycle, the diode is reverse biased and the whole input voltage appears across the diode. When the input reaches its peak value V<sub>m</sub>, in the negative half cycle, the voltage across the diode is maximum. This is the PIV of the given diode. In rectifier design two important parameters must be considered.

1. The current handling capacity required of the diode

2. Peak Inverse Voltage that the diode must withstand without breakdown. It is desirable to select a diode having reverse breakdown voltage at least 50% more than that the expected PIV.

# PROBLEM

The turn ratio of the transformer used in a bridge rectifier is 12:1. The primary is connected to 220V, 50 Hz power. Assuming the diodes to be ideal, find the dc voltage across the load. What is the PIV of each diode?

Given:  $V_{rms} = 220 V$

Maximum primary voltage= $V_P = \sqrt{2} V_{rms} = 311 V$

If the maximum secondary voltage is  $\mathit{V\!s}$  , then

$$\frac{V_P}{V_S} = \frac{12}{1}$$

(since the turn ratio is 12:1)

:

$$V_s = V_P \frac{1}{12} = \frac{311}{12} = 25.9$$

volts

$$PIV = V_s = 25.9 V$$

d.c.voltage across the load= $V_{dc} = \frac{2V_s}{\pi} = \frac{2 \times 25.9}{3.14} = 16.48 V$

### PROBLEM

A power supply delivers 90 watts to a load of 1 kilo ohms. Find the a.c. voltage present across the load, if the ripple factor is 0.1%

Power delivered to the load

$$P = \frac{V^2}{R} \quad or \quad V = \sqrt{PR}$$

$$= \sqrt{90 \times 1000} = 300 V \quad \text{since P=90 and R=1000}$$

$$\therefore V_{dc} = 300V$$

Ripple factor  $\gamma = \frac{V_{ac}}{V_{dc}}$  or  $V_{ac} = r \times V_{dc} = \frac{0.1}{100} \times 300 = 0.3 \text{ V}$

#### 1.14 Diode Clipping Circuits

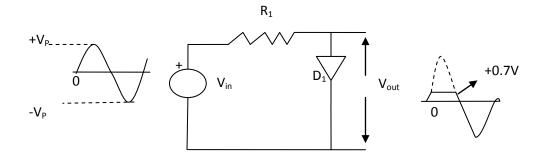

The Diode Clipper, also known as a *Diode Limiter*, is a wave shaping circuit. It prevents the output of a circuit from exceeding a predetermined voltage level without distorting the remaining part of the applied waveform. It consists of resistors, junction diodes or transistors. Clipping is achieved either at one level or two levels.

#### (a) **Positive Diode Clipping Circuits**

In this diode clipping circuit fig. 1.12, the diode is forward biased during the positive half cycle of the sinusoidal input waveform. For the silicon diode to become forward biased, it

must have the input voltage magnitude greater than +0.7 volts (+0.3 volts for a germanium diode). When this happens the diode begins to conduct and holds the voltage across itself

Fig. 1.12

constant at 0.7V until the sinusoidal waveform falls below this value. Thus the output voltage which is taken across the diode can never exceed 0.7 volts during the positive half cycle. During the negative half cycle, the diode is reverse biased (cathode more positive than anode) blocking current flow through itself and as a result has no effect on the negative half of the sinusoidal voltage which passes to the load unaltered. Thus the diode limits the positive half of the input waveform and is known as a positive clipper circuit.

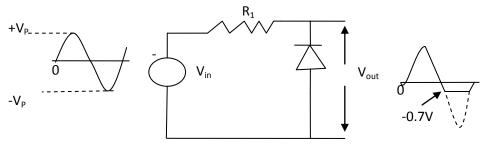

### (b) Negative Diode Clipping Circuits

Here the reverse is true (fig. 1.13). The diode is forward biased during the negative half cycle of the sinusoidal waveform and limits or clips it to -0.7 volts while allowing the positive half cycle to pass unaltered when reverse biased. As the diode limits the negative half cycle of the input voltage it is called a negative clipper circuit.

Fig. 1.13

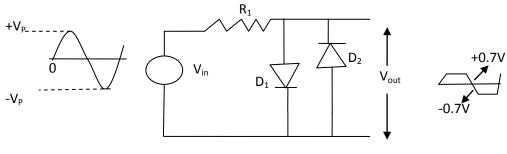

#### (c) Clipping of both half cycles

If we connect two diodes in inverse parallel as shown in fig. 1.14, then both the positive and negative half cycles would be clipped as diode  $D_1$  clips the positive half cycle of

Fig. 1.14

the sinusoidal input waveform while diode  $D_2$  clips the negative half cycle. Then diode clipping circuits can be used to clip the positive half cycle, the negative half cycle or both. For ideal diodes the output waveform above would be zero. However, due to the forward bias voltage drop across the diodes the actual clipping point occurs at +0.7 volts and -0.7 volts respectively. But we can increase this ±0.7V threshold to any value we want up to the maximum value, ( $V_{PEAK}$ ) of the sinusoidal waveform either by connecting together more diodes in series creating multiples of 0.7 volts, or by adding a voltage bias to the diodes.

### 1.15 Positive Biased Diode Clipping Circuits

To produce diode clipping circuits for voltage waveforms at different levels, a bias voltage,  $V_{Bias}$  is added in series with the diode as shown in fig. 1.15. The voltage across the series combination must be greater than  $V_{Bias}$  + 0.7V before the diode becomes sufficiently forward biased to conduct. For example, if the  $V_{Bias}$  level is set at 4.0 volts, then the sinusoidal voltage at the diode's anode terminal must be greater than 4.0 + 0.7 = 4.7 volts for it to become forward biased. Any anode voltage levels above this bias point are clipped off.

Fig. 1.15

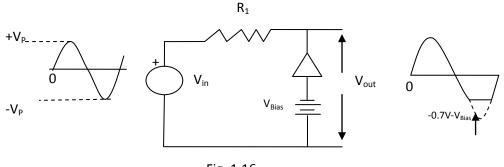

### (b) Negative Biased Diode Clipping circuits

Likewise, by reversing the diode and the battery bias voltage, when a diode conducts the negative half cycle of the output waveform is held to a level  $-V_{BIAS} - 0.7V$  as shown in fig. 1.16

Fig. 1.16

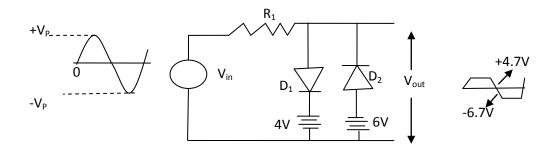

#### (c) Biased Diode Clipping of both levels

If both the positive and the negative half cycles are to be clipped, then two biased clipping diodes are used. But for both positive and negative diode clipping, the bias voltage need not be the same. The positive bias voltage could be at one level, for example 4 volts, and the negative bias voltage at another, for example 6 volts as shown in fig. 1.17.

When the voltage of the positive half cycle reaches +4.7 V, diode  $D_1$  conducts and limits the waveform at +4.7 V. Diode  $D_2$  does not conduct until the voltage reaches -6.7 V. Therefore, all positive voltages above +4.7 V and negative voltages below -6.7 V are automatically clipped.

Fig. 1.17

The advantage of biased diode clipping circuits is that it prevents the output signal from exceeding preset voltage limits for both half cycles of the input waveform, which could be an input from a noisy sensor or the positive and negative supply rails of a power supply. If the diode clipping levels are set too low or the input waveform is too great then the elimination of both waveform peaks could end up with a square-wave shaped waveform.

# **Uses of Clipping circuits**

- 1. They are used to change the shape of a waveform

- 2. They are used in Circuit transient protection

- 3. They are used in speech processing for communication

- 4. They are used to chopp the overall signal down to size so that the excessive amplitude does not overload the subsequent stages and cause a malfunction

- 5. Diode clipping circuits can be used in voltage limiting applications.

# 1.16 Diode Clamping Circuits

Clampers can also be referred as DC restorers. Clamping circuits are designed to shift the input waveform either above or below the DC reference level without altering the shape of waveform. This shifting of the waveform results in a change in the DC average voltage of the input waveform. The levels of peaks in the signal can be shifted using the clamper circuit, hence clampers can also be referred as level shifters. Clampers can be broadly classified into two types. They are positive clampers and negative clampers.

1. **Positive Clamper:** This type of clamping circuit shifts the input waveform in the positive direction, as a result the waveform lies above a DC reference voltage.

2. **Negative Clamper:** This type of clamping circuit shifts the input waveform in the negative direction, as a result the waveform lies below a DC reference voltage.

The direction of the diode in the clamping circuit determines the type of clamper circuit. The operation of a clamping circuit is mainly based on the switching time constants of the capacitor. However, capacitor in the circuit charges through the diode and discharges through the load.

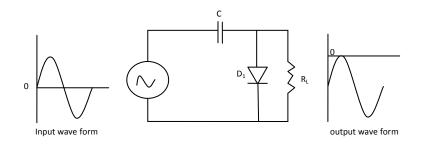

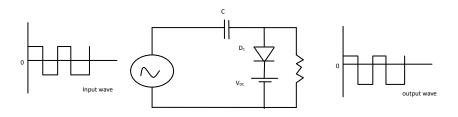

#### (a) Negative Clamper

The Negative Clamping circuit consists of a diode connected in parallel with the load (fig. 1.18) The capacitor used in the clamping circuit can be chosen such that it must charge very quickly and it should not discharge very drastically. The anode of the diode is connected to the capacitor and cathode to the ground. During the positive half cycle of the

Fig. 1.18

input, the diode is in forward bias and as the diode conducts the capacitor charges very quickly. During the negative half cycle of the input, the diode will be in reverse bias and the diode will not conduct, the output voltage will be equal to the sum of the applied input voltage and the charge stored in the capacitor during reverse bias. The output waveform is same as input waveform, but shifted below 0 volts.

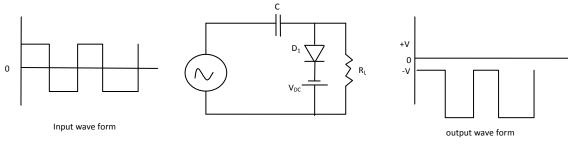

# (b) Negative Clamper with Positive Reference Voltage

The circuit arrangement is very similar to the negative clamper circuit, but a DC reference supply is connected in series with the diode (fig. 1.19). The output waveform is also similar to the negative clamper output waveform, but it is shifted towards the negative direction by an amount equal to the reference voltage at the diode.

Fig. 1.19

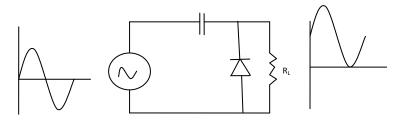

# c) Negative Clamper with negative reference voltage

If the reference voltage directions in the above circuit are reversed (fig. 1.20) and connected to the diode in series, then during the positive half cycle the diode starts conducting current before applying input voltage. Since the cathode has a very small negative reference voltage less than zero volts, the waveform is shifted away from the 0 volts towards the negative direction by an amount of the reference voltage.

Fig. 1.20

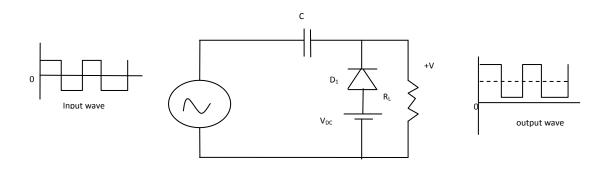

# 1.17 Positive Clamper

The circuit of the positive clamper is similar to the negative clamper but the direction of the diode is inverted in such a way that the cathode of the diode is connected to the capacitor (fig. 1.21)

Fig. 1.21

During the positive half wave cycle, output voltage of the circuit will be the sum of applied input voltage and the charge stored at capacitor. During the negative half wave cycle, the diode starts to conduct and charges the capacitor very quickly to its maximum value. The output waveform of the positive clamper shifts towards the positive direction above the 0 volts.

# (a) Positive Clamper with Positive Reference Voltage

A positive reference voltage is connected in series with the diode in the positive clamper circuit (fig. 1.22) such that the positive terminal of the reference voltage is connected in series with the anode of the diode. During the positive half wave cycle of the input sinusoidal waveform, the diode starts conducting, because initially the supply voltage is less than the diode's anode positive reference voltage. If once the cathode voltage is greater than anode voltage, the diode stops conduction of electric current. During the negative half cycle, the diode conducts and charges the capacitor very quickly.

Fig. 1.22

#### (b) Positive Clamper with Negative Reference Voltage

The direction of the reference voltage is reversed in this case (fig. 1.23) such that the negative terminal of the reference voltage is connected in series with the anode of diode reflecting it as a negative reference voltage. During the positive half wave cycle of the input waveform, the diode does not conduct, as a result the output is equal to voltage stored in the capacitor and applied input voltage. During the negative half cycle, the diode starts conducting current after the cathode voltage value is less than the anode voltage and we get the waveform as shown.

Fig. 1.23

#### 1.18 Features of clamping circuits

The shape of the waveform will be the same, but its level is shifted either upward or downward direction.

- 2) There will be no change in the peak-to-peak or rms value of the waveform due to the clamping circuit.

- 3) There will be a change in the peak and average values of the waveform.

- 4) The values of the resistor R and capacitor C affect the waveform.

- 5) The values for the resistor R and capacitor C should be determined from the time constant equation of the circuit, t = RC. In a good clamper circuit, the circuit time constant T = RC should be at least ten times the time period of the input signal voltage.

# 1.19 Uses

- 1) Clamping circuits are often used in television receivers as dc restorers.

- They are used in analogue video processing to define portions of luminance wave form (black level)

- 3) They are used in Method of modulating AM transmitters

- 4) Clamping circuits are sometimes used in the bias circuits of oscillators or in automatic gain control (AGC) circuits.

- 5) Clampers are widely used in test equipments and other sonar systems.

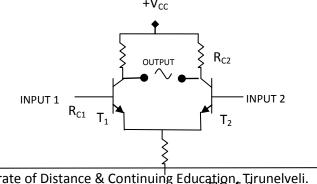

# **UNIT II : TRANSISTORS AND AMPLIFIERS**

Transistors – Transistor action – three modes of connection – biasing – load line and Q – point – voltage divider bias – stabilization – CE amplifier.

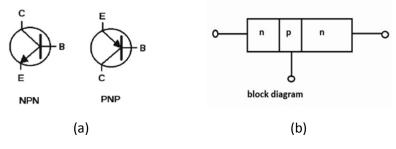

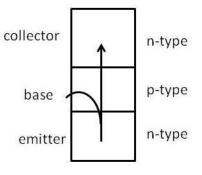

### 2.1 TRANSISTORS

The transistor is the fundamental building block of modern electronic devices. It is a semiconductor device used to amplify or switch electronic signals and electrical power. It is composed of semiconductor material usually with at least three terminals for connections. Voltage or current applied to one pair of the transistor's terminals changes the current through another pair of terminals. Because the controlled output power can be higher than the controlling input power, a transistor amplifies a given signal . The symbol used for a transistor are shown in the fig. 2.1. A transistor has three regions namely, Emitter, Base and Collector. Base region is the thinnest of all. Collector is wider than both Emitter and Base.

Fig. 2.1

Emitter is heavily doped so that it can eject large amount of charge carriers. Base is lightly doped so that it passes most of the charge carriers into collector. The collector is moderately doped.

### **Transistor Biasing**

Transistor Biasing is the process of setting a transistor to dc operating voltage or current conditions to the correct level so that any ac input signal can be amplified correctly by the transistor. Establishing the correct operating point requires the proper selection of bias

resistors and load resistors to provide the appropriate input current and collector voltage conditions. The correct biasing point for a bipolar transistor, either npn or pnp, generally lies somewhere between the two extremes of operation with respect to it being either "fully-ON" or "fully-OFF" along its load line. This central operating point is called the *Quiescent Operating Point*, or *Q-point* for short. With a single resistor usage, the biasing voltages and currents do not remain stable during transistor operation and can vary enormously. Also the temperature of the transistor can adversely affect the operating point.

# 2.2 Bias Stabilisation

It should be ensured that the operating point of a transistor is fixed at a suitable point. If it is shifted then the transistor will be driven to undesired regions and the circuit will become unreliable. The following are the reasons for the shift of operating point.

- i. Variation of transistor parameters with temperature

- ii. Parameter change from one transistor to another.

Collector current produces heat at base-collector junction. This will increase the number of minority charge carriers at the reverse biased B-C junction and the leakage current increases. This inturn will increase the collector current. The cycle repeats again. So, the transistor will reach the saturation region. The excess heat produced sometimes damage the transistor. This situation is called *thermal runaway*.

# **Stability factor**

Stability factor is defined as the rate of change of collector current with respect to collector leakage current keeping the current gain  $\beta$  and base current I<sub>B</sub> constant.

*ie.* Stability factor

$$S = \left(\frac{dI_C}{dI_{co}}\right)_{\beta, I_B}$$

(2.1)

where  $I_{co}$  is the collector leakage current.

# 2.3 Expression for Stability factor for C.E. configuration:

In C. E. configuration,

Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli.

Collector current  $I_c = \beta I_B + (\beta + 1)I_{co}$

Differentiating w.r.t.  $I_c$  , we can write

$$1 = \beta \frac{dI_B}{dI_c} + (\beta + 1) \frac{dI_{co}}{dI_c}$$

But stability factor  $S = \left(\frac{dI_C}{dI_{co}}\right)_{\beta I_c}$

$$\therefore 1 = \beta \frac{dI_B}{dI_c} + (\beta + 1) \frac{1}{S}$$

or

$$(\beta + 1)\frac{1}{S} = 1 - \beta \frac{dI_B}{dI_c}$$

or  $S = \frac{\beta + 1}{1 - \left(\beta \frac{dI_B}{dI_c}\right)}$

(2.2)

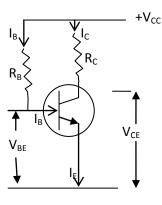

#### 2.4 Fixed bias

Using a suitable resistance across the base of a transistor (fig. 2.2) a fixed amount of current

may be passed through the base and hence this is called a fixed bias. In this circuit a resistance  $R_B$  is connected between the base and the positive terminal of the supply  $V_{CC}$ . Applying Kirchoff's voltage law to the base-emitter-ground loop we get,

Fig.2.2

Where  $I_B$  is the base current and  $V_{BE}$  the base emitter voltage. From the above eqn.

$$I_B R_B = (V_{CC} - V_{BE}) \quad or \quad I_B = (V_{CC} - V_{BE}) / R_B$$

(2.3)

$= V_{CC} / R_B$ , if  $V_{BE}$  is very small. Since the supply voltage  $V_{CC}$ , base resistor  $R_B$  are fixed, the base current is also fixed.

# Advantages

- 1) It a simple circuit to construct

- 2) The biasing conditions can be easily achieved

- Since there is no resistance between base and emitter, no loading of the source by the biasing current is reached

# Disadvantages

- 1) Stability factor is high resulting in quick thermal runaway

- 2) Poor stabilisation

### 2.5 Voltage divider biasing

The voltage divider is formed using external resistors  $R_1$  and  $R_2$  (fig. 2.3). The voltage across  $R_2$  forward biases the emitter junction. By proper selection of resistors  $R_1$  and  $R_2$ , the operating point of the transistor can be made independent of feedback factor  $\beta$ . In this circuit, the voltage divider holds the base voltage fixed independent of base current provided the divider current is large compared to the base current. From the circuit,

$$\downarrow \mathbf{I}_{1} \overset{+ V_{CC}}{\underset{V_{BE}}{}} \downarrow \mathbf{I}_{C}} \downarrow \mathbf{I}_{C}$$

$I_1 = \frac{V_{CC}}{R_1 + R_2}$

Voltage dropped across R<sub>2</sub> is given by

$$V_2 = \left(\frac{V_{CC}}{R_1 + R_2}\right) R_2$$

Using Kirchoff's voltage law to the base circuit,

$$V_{2} = V_{BE} + V_{E}$$

=  $V_{BE} + I_{E}R_{E}$

or  $I_{E} = \frac{V_{2} - V_{BE}}{R_{E}}$

Or  $I_{C} = \frac{V_{2} - V_{BE}}{R_{E}}$  since,  $I_{E} = I_{C}$

Thus, I<sub>c</sub> is independent of transistor parameters and hence good stabilisation is ensured. This is the universal method providing transistor biasing.

# Advantages of voltage divider biasing circuits

- 1) Only one dc supply is necessary.

- 2) Operating point is almost independent of  $\beta$  variation.

- 3) Operating point is stabilized against shift in temperature.

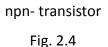

### 2.6 Transistor action

Transistor operation is basically the action of a relatively small emitter-base bias voltage controlling a relatively large emitter-to-collector current. The current flow in the external circuit is always due to the movement of free electrons. The

transistor can be considered as two p-n junctions that are placed back to back. The structure has two p-n junctions with a narrow base region between collector and emitter. In normal operation, the base emitter junction is forward biased and the base collector junction is reverse biased. When a current flows through the base emitter junction, a current also flows in the collector circuit. This is larger and proportional to the one in the base circuit. In order to explain the way in which this happens, the example of an n-p-n transistor is taken. The same principles is used for the p-n-p transistor except that the current carrier is holes and the voltages are reversed.

The emitter in the n-p-n device is made of n-type material and here the majority carriers are electrons. When the base emitter junction is forward biased the electrons move from the n-region towards the p- region and the holes move towards the n- region. This enables a current to flow across the junction. When the junction is reverse biased the holes and electrons move away from one another resulting in a depletion region between the two areas and no current flows.

#### Operation of a bipolar junction transistor

When a current flows between the base and emitter, electrons leave the emitter and flow into the base. Normally the electrons would combine when they reach this area. However the doping

Fig. 2.5

level in this region is very low and the base is also very thin. This means the most of the electrons are able to travel across this region without recombining with the holes. As a result the electrons migrate towards the collector, because they are attracted by the positive potential. In this way they are able to flow across and current flows in the collector circuit. It is found that the collector current is significantly higher than the base current, and because the proportion of electrons combining with holes remains the same the collector current is always proportional to the base current. In other words varying the base current varies the collector current. The ratio of the base to collector current  $\left(\frac{I_B}{I_C}\right)$  is given the Greek symbol  $\beta$ . Typically the ratio  $\beta$  may be between 50 and 500 for a small signal transistor. The ratio between collector current and emitter current  $\left(\frac{I_C}{I_B}\right)$  is called  $\beta$  of the transistor.

# **2.7** Relation between $\alpha$ and $\beta$ of a transistor

The sum of base current and collector current is equal to the emitter current.

ie.

$$I_E = I_B + I_C$$

or  $I_C = I_E - I_B$

From definition  $\alpha = \left(\frac{I_C}{I_E}\right) = \left(\frac{I_E - I_B}{I_E}\right)$

$= \frac{(I_E/I_C) - (I_B/I_C)}{(I_E/I_C)} = \frac{(1/\alpha) - (1/\beta)}{(1/\alpha)}$

cross multiplying,

$$\alpha \left(\frac{1}{\alpha}\right) = \left(\frac{1}{\alpha}\right) - \left(\frac{1}{\beta}\right)$$

or  $\left(\frac{1}{\alpha}\right) - \left(\frac{1}{\beta}\right) = 1$  (2.4)

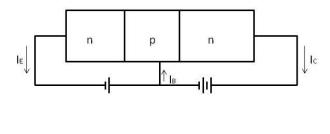

### 2.8 Different modes of connections

There are three basic configurations of transistors namely, Common Base (CB), Common Emitter (CE) and Common Collector (CC) modes used in electronic circuits. Some important characteristics of these different modes or configurations are given below. Based on these they are used for different applications. Figure (2.6) depicts all the three transistor configurations used in various applications of electronic circuit.

### (i) Common Base (C.B.) Mode

Common base mode (fig. 2.6a) is usually used for VHF and UHF amplifiers where, although the voltage gain is not high, there is little chance of the output signal being fed back into the input circuit . Because the base of the transistor is connected to ground in this mode, it forms an effective grounded screen between output and input. As the collector current in this mode is the emitter current minus the base current, the current gain ( $h_{fb}$  in common base mode) is less than unity.

### **Characteristics**

- a. It has low input impedance (on the order of 50 to 500 Ohms).

- b. It has high output impedance (on the order of 1 to 10 Mega Ohms).

- c. Current gain ( $\alpha$ ) is less than unity.

# (ii) Common Emitter (C.E) mode

The most common function of a transistor is the common emitter mode (fig. 2.6b). In this method of connection small changes in base or emitter current cause large changes in collector or emitter current. Therefore the circuit is that of a current amplifier. To give voltage amplification, a load resistor must be connected in the collector circuit, so that a change in collector current causes a change in the voltage developed across the load resistor. The output waveform will be 180 degree out of phase to the input waveform.

### Characteristics

- 1. It has high input impedance (on the order of 500 to 5000 Ohms).

- 2. It has low output impedance (on the order of 50 to 500 Kilo Ohms).

- 3. Current gain ( $\beta$ ) is 98.

- 4. Power gain is upto 37 dB.

- 5. Output is 180 degree out of phase.

### (iii) Transistor Common Collector (C. C) mode

The C.E. mode also called the emitter follower is shown in the fig. 2.6(c). The output waveform at the emitter is not inverted and so follows the input waveform at the base.

This method of connection is often used as a buffer amplifier for such jobs as matching impedances between two other circuits. This is because this mode gives the amplifier a high input impedance and a low output impedance. The voltage gain in this mode is slightly less than unity, but high current gain is available. Another use for this mode of connection is a current amplifier, often used for output circuits that have to drive high current AC devices such as loudspeakers or DC devices such as motors etc.

# Characteristics

- 1. It has high input impedance (on the order of about 150 to 600 Kilo Ohms).

- 2. It has low output impedance (on the order of about 100 to 1000 Ohms).

- 3. Current gain ( $\beta$ ) is about 99.

- 4. Voltage and power gain is equal to or less than one.

Following table summarizes important points about CB, CE, CC transistor configurations.

| Parameter        | C.B              | C.E               | C.C             |  |

|------------------|------------------|-------------------|-----------------|--|

| Voltage Gain     | High, same as CE | High              | Less than Unity |  |

| Current Gain     | Less than Unity  | High              | High            |  |

| Power Gain       | Moderate         | High              | Moderate        |  |

| Phase inversion  | No               | Yes               | No              |  |

| Input Impedance  | Low (50 Ω)       | Moderate(1K Ω)    | High (300 K Ω)  |  |

| Output Impedance | High (1 MΩ)      | Moderate (50 K Ω) | Low (300 Ω)     |  |

# Comparison between C.E., C.B., C.C. connections of a transistor

#### 2.9 Transistor Static characteristics in C.E mode

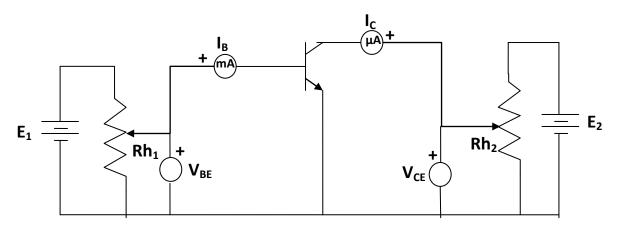

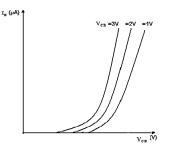

The basic circuit diagram for studying the characteristics of a given transistor is shown in the fig. 2.7. The input is applied between base and emitter, the output is taken between collector and emitter. Here the emitter of the transistor is common to both input and output and hence called CE mode. Input characteristics are obtained between the input current and input voltage at constant output voltage ( $V_{CE}$ ). It is plotted between  $V_{BE}$  and  $I_B$  at constant  $V_{CE}$  in CE configuration. Output characteristics are obtained between ( $I_B$ ). It is plotted between the output voltage and output current at constant input current ( $I_B$ ). It is plotted between  $V_{CE}$  and  $I_C$  at constant  $I_B$  in CE configuration.

#### Experiment

#### **Input Characteristics**

Connections are made as shown in the circuit diagram (fig. 2.7). Output voltage is kept at  $V_{CE} = 0V$  by varying the rheostat ( $R_{h2}$ ). By using the rheostat ( $R_{h1}$ ),  $V_{BE}$  is gradually varied and the base current  $I_B$  and base-emitter voltage  $V_{BE}$  are noted. Initially  $V_{BE}$  is varied in steps of 0.1 V. Once the current starts increasing it is varied in steps of 1V up to 12V. The procedure is repeated for  $V_{CE} = 2V$ , 3V etc.

Fig. 2.7

#### **Output Characteristics**

To study the output characteristics, base current is fixed at (say)  $I_B = 20 \,\mu$ A .  $V_{CE}$  is gradually varied in steps of 1V up to 12V and collector current  $I_C$  and Collector-Emitter Voltage  $V_{CE}$  are noted. This procedure is repeated for  $I_B = 40 \,\mu$ A,  $60\mu$ A, etc. The readings are Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli.

tabulated as shown and suitable graphs are drawn. The various parameters related are calculated using the following formula

Input resistance

$$r_i = \left(\frac{\Delta V_{BE}}{\Delta I_B}\right)_{V_{CE}}$$

Output resistance  $r_0 = \left(\frac{\Delta V_{CE}}{\Delta I_C}\right)_{I_B}$

Current gain  $\beta = \left(\frac{I_C}{I_B}\right)_{V_{CE}}$

#### **Input Characteristics**

| V <sub>CE</sub> =1V    |                       | V <sub>CE</sub> =2V |                       | V <sub>CE</sub> =3V |                       |

|------------------------|-----------------------|---------------------|-----------------------|---------------------|-----------------------|

| V <sub>BE(Volts)</sub> | I <sub>B</sub> ( μA ) | $V_{BE(Volts)}$     | I <sub>B</sub> ( μA ) | $V_{BE(Volts)}$     | I <sub>в</sub> ( μA ) |

|                        |                       |                     |                       |                     |                       |

|                        |                       |                     |                       |                     |                       |

|                        |                       |                     |                       |                     |                       |

(2.5)

# Output Characteristics

| I <sub>B</sub> =0 μΑ |        | I <sub>B</sub> =20 μΑ  |        | I <sub>B</sub> =40 μΑ |        |

|----------------------|--------|------------------------|--------|-----------------------|--------|

| $V_{CE(Volts)}$      | lc(mA) | V <sub>CE(Volts)</sub> | lc(mA) | $V_{CE(Volts)}$       | lc(mA) |

|                      |        |                        |        |                       |        |

|                      |        |                        |        |                       |        |

|                      |        |                        |        |                       |        |

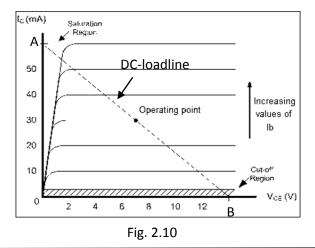

# 2.10 Quiescent Point (Q-Point)

In an amplifier to get faithful amplification, suitable bias resistance and voltage values must be selected for the given transistor. This condition gives a set of d.c. voltage and current values in the transistor under zero signal condition. This is known as the *operating point or* Q- *point*. It is a point on the dc load line which represents dc collector – emitter voltage

$(V_{CE})$  and collector current  $(I_C)$  in the absence of ac single. It is also called the operating point because the variations in  $V_{CE}$  and  $I_C$  take place about this point when signal is applied. The best position for this point is midway between cut-off and saturation points where  $V_{CE} = 1/2 V_{CC}$ . Q - Point marked on the output characteristics curve. Q-point shifts up and down along the ac load line when changes in output voltage and current of an amplifier are caused by an ac signal

### Significance of Q - point in transistor

Normally whatever signals we want to amplify will be of the order milli volts or less. If we directly input these signals to the amplifier they will not get amplified as transistor needs voltages greater than cut in voltages for it to be in active region. Only in active region of operation transistor acts as amplifier. So we can establish appropriate DC voltages and currents through transistor by external sources so that the transistor operates in active region and superimpose the AC signals to be amplified. The DC voltage and current are so chosen that the transistor remains in active region for entire AC signal. All the input AC signals variations happen around Q-point. The points where the characteristic curve and the load line intersect are the possible operating points or Q points. To maintain the transistor at Q value for all operating signal values, suitable biasing is done.

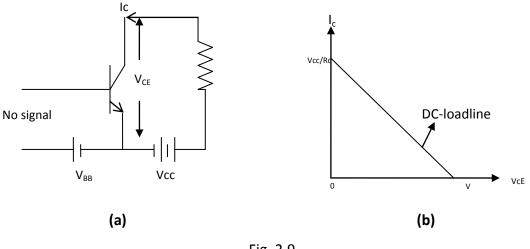

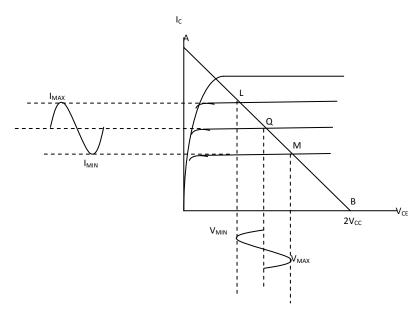

### 2.11 Load line analysis

To draw DC load line of a transistor, we need to find the saturation current and cutoff voltage. The saturation current is the maximum possible current through the transistor and occurs at the point where the voltage across the collector is minimum. The cutoff voltage is the maximum possible voltage across the collector and occurs at zero collector current. A common emitter amplifier circuit is shown in the fig. 2.9(a). When collector current Ic=0, the collector-emitter voltage is maximum and is equal to Vcc.

Maximum  $V_{CE} = V_{CC} - R_C I_C$

$$\therefore (V_{CE})_{\max} = V_{CC} \text{ since, } I_c = 0$$

2.6(b)

This gives the cut off point  $(V_{CE}, 0)$  on X-axis [fig. 2.9(b)]

When collector emitter voltage  $V_{CE} = 0$ , the collector current is maximum and is equal to

$V_{CC} / R_C$  ·

$\therefore 0 = V_{CC} - I_C R_C$ Maximum  $I_C = V_{CC} / R_C$

This gives the cut off point on Y-axis. Joining these two points gives the dc load line.

### **Operating point**

The zero signal values of Ic and Vce are known as operating point. The variations of Ic and  $V_{CE}$  take about this point when signal is applied. Let, in the absence of signal the base current is 10  $\mu$ A. Then Ic and  $V_{CE}$  condition are represented by some point on dc load line AB. Q-point is the point where the load line and the characteristic curve intersect

Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli. 35

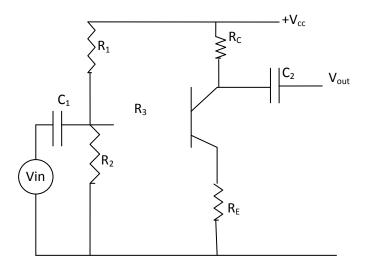

### 2.12 CE Amplifier

In electronics, a common emitter amplifier is one of the three basic single-stage bipolarjunction-transistor (BJT) amplifier topologies, typically used as a voltage amplifier. In this circuit, the base terminal of the transistor serves as the input, the collector is the output and the emitter is common to both.

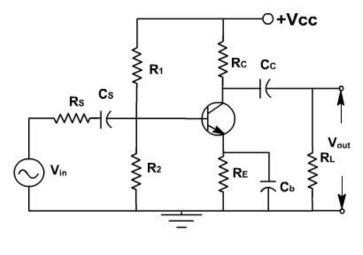

#### Construction

A basic C.E. transistor amplifier circuit using a pnp transistor is shown in the fig. (2.11).  $R_1$  and  $R_2$  form the potential divider biasing for the transistor. To compensate the variation of collector current, a resistance  $R_E$  is connected at the emitter. To eliminate the variation of voltage across  $R_E$ , a capacitor  $C_E$  is connected parallel to RE. Cs prevents any dc flow into the input. Cc is the coupling capacitor to the next stage.

#### Working:

When an ac input signal is applied at the base, the output is obtained at the collector across the load  $R_L$ . There is a phase change of 180 degree between the input and output of this amplifier. For example, if the input signal increases it induces a small increase in base

current. This will cause a large change in collector current due to transistor action. This large change in collector current causes a large change in voltage across the load. Thus a weak signal is amplified at the output. We can draw a series of curves that show the Collector

Fig. 2.11

current, Ic against the Collector-Emitter voltage ( $V_{CE}$ ) with different values of base current, Ib. These curves are known as the Output Characteristic Curves and are used to show how the transistor will operate over its dynamic range. When the transistor is switched "OFF",  $V_{CE}$  equals the supply voltage Vcc and this is point B on the line. Likewise

when the transistor is fully "ON" and saturated the Collector current is determined by the load. resistor,  $R_L$  and this is the point A on the line. Point Q on the load line gives the base current. As the load line cuts through the different base current values on the DC characteristics curves we find the peak swings of base current that are equally spaced along the load line. These values are marked as points L and M on the line, Any input signal giving a base current greater than this value will drive the transistor to go beyond point M and into its "cut-off" region or beyond point L and into its saturation region thereby resulting in distortion to the output signal in the form of "clipping". Using points L and M as an example, the instantaneous values of collector current and corresponding values of collector-emitter voltage can be projected from the load line. It can be seen that the collector-emitter voltage is in anti-phase (-180°) with the collector current. As the base current  $I_B$  changes in a positive direction the collector-emitter voltage, or the output voltage decreases from its steady state value. Thus a single stage Common Emitter Amplifier is also called an inverting amplifier.

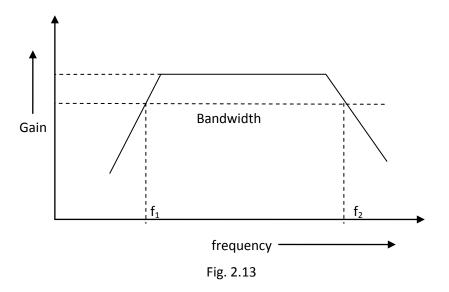

#### 2.13 Frequency response curve

The variation of the gain of the amplifier with frequency is shown in the fig. 2.12. This response is called frequency response curve. At low frequencies of the input signal, the gain increases. In the middle range it is constant. At high frequency range the gain again

decreases. 0.707 times the maximum gain value cut the curve at two points called low cutoff ( $f_1$ ) and high cut off ( $f_2$ ) frequencies. ( $f_2$ - $f_1$ ) gives the bandwidth of the amplifier.

# Special features of CE amplifier

- 1. Input impedance is low

- 2. Output impedance is high

- 3. Input and out are 180 degree out of phase

- 4. Voltage gain and current gains are high

# **UNIT III : OSCILLATORS**

Principles of negative voltage feed back in amplifiers – gain – advantages – principle of negative current feedback – Oscillation – Bark Hausen criterion for oscillation – colpitt's oscillator

# 3.1 Feedback Circuits

Feedback loops are used to control the output of electronic circuits. A feedback loop is created when all or some portion of the output is fedback to the input. There are two types of feedback circuits. They are positive feedback circuits and negative feedback circuits.

# (i) Negative feedback

A negative feedback circuit is an electronic circuit that subtracts a fraction of its output from its input, so that it opposes the original signal. The applied negative feedback improves the performance by the ways of gain stability, linearity, frequency response, step response and reduces sensitivity to parameter variations due to manufacturing or environment. Because of these advantages, many amplifiers and control systems use negative feedback.

# (ii) Positive feedback

When the feedback energy which may be voltage or current, is in phase with the input signal then it is called positive feedback. In this case, both amplifier and the feedback circuit introduce each a phase shift of 180<sup>°</sup>. The net result is 360<sup>°</sup> phase shift around the loop.

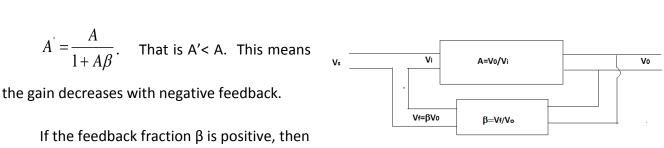

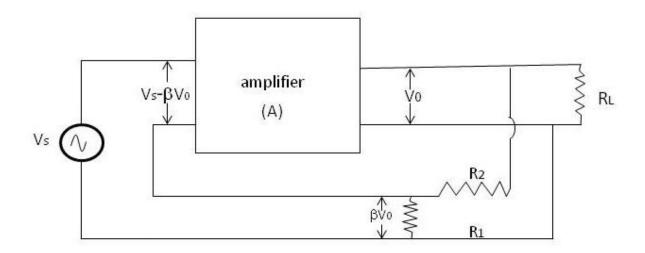

# 3.2 Effect of negative feed back

Let  $V_0$  be the output voltage and  $V_i$  is the input voltage of an amplifier.

Then the gain of the amplifier is

$$A = \frac{V_0}{V_i}$$

. (3.1)

Now using a feedback network, let a fraction of the output ( $\beta$ ) is fedback to the input.

Now the total input voltage is

$$V_i = V_s + \beta V_0$$

(3.2)

From eqn 3.1,

$$V_0 = AV_i$$

or  $V_i = \frac{V_0}{A}$

Substituting this in eqn. (3.2), we get

$$\frac{V_0}{A} = V_s + \beta V_0$$

$$V_0 = AV_s + A\beta V_0$$

$$V_0(1 - A\beta) = AV_s$$

$$\frac{V_0}{V_s} = A' = \frac{A}{1 - A\beta}$$

(3.3)

This gives the gain of the amplifier with feedback.

If the feed back fraction  $\boldsymbol{\beta}$  is negative then the gain with negative feedback is,

$A' = \frac{A}{1 - A\beta}$ . That is A'>A or the gain increases with positive feedback.

If A $\beta$ =1, then  $A' = \frac{A}{1 - A\beta} = \infty$ . That is the gain becomes infinite. In other words

there is output even if there is no input. This forms an oscillator. The amplifier introduces a phase difference of  $180^{\circ}$ . If the feedback network produces another phase difference of  $180^{\circ}$ , totally there will be a phase difference of  $360^{\circ}$ . This kind of feed back is called regenerative feedback. So, the conditions for continuous oscillations may be stated as,

- 1. the feed back factor A $\beta$ =1

- 2. feedback must be positive

The above conditions are called *Barkhausen criterion* for oscillation.

# 3.3 Advantages of negative feedback amplifier

1. **Gain stability:** The negative feedback amplifier increases the Gain Stability. The gain will be stable over external or internal variations.

- Noise reduction: By using negative feedback amplifier we can reduce the noise level to some extent

- 3. **Increase of Bandwidth:** Negative feedback amplifier decreases the Voltage gain, the reduction in voltage gain results improved Frequency Band Width.

- 4. **Increase in input impedence:** The amplifier with negative feedback Increases the Input impedence. Thus we can avoid loading of signal source.

- 5. Decrease in output impedence: Negative feedback decreases its output impedence

Problem: The gain of an amplifier is 120. When negative voltage feedback is applied, the gain is reduced to 20. Find the feedback ratio?

Given: A = 120; A' = 20;  $\beta = ?$

We know that the gain of an amplifier with negative feedback is  $A' = \frac{A}{1 + A\beta}$

Substituting the values,

$$20 = \frac{120}{1+120\beta}$$

or  $20+2400\beta = 120$

Or

$$\beta = \frac{100}{2400} = \frac{1}{24}$$

.

So, the feedback ratio= $\frac{1}{24}$

## 3.4 Effect of negative feedback on the stability of an amplifier

Eventhough the negative feedback reduces the gain of an amplifier, it increases the stability.

Consider an amplifier with negative feedback. Its closed loop gain is given by

$$A' = \frac{A}{1 + A\beta} \tag{3.4}$$

If feedback fraction  $\beta$  is very large, then we can assume  $1 + A\beta = A\beta$

From eqn. (3.4),

$$A' = \frac{A}{1+A\beta} = \frac{A}{A\beta} = \frac{1}{\beta}$$

(3.5)

So the gain is depending only on the feedback fraction  $\beta$ , which depends on feedback network, and is independent of any other amplifier parameters. Thus negative feedback improves the stability of the amplifier.

## 3.5 Feedback circuit

The network used for providing negative voltage feedback is shown in the fig. 3.2. It consists of a potential divider arrangement by using two resistors  $R_1$  and  $R_2$ . The output voltage of

Fig. 3.2

the amplifier is fed across this arrangement. By choosing suitable values for the resistors, a required negative feedback is obtained.

From the circuit, voltage across

$$R_1 = rac{V_0}{R_1 + R_2} imes R_1$$

Feedback fraction

$$\beta = \frac{\text{voltage} \quad \text{across} \quad R_1}{V_0} = \frac{R_1}{R_1 + R_2}$$

(3.6)

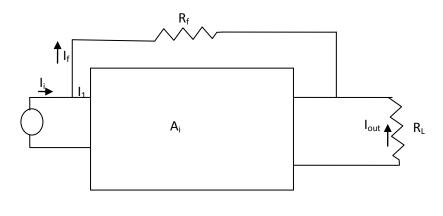

#### 3.6 Principle of negative current feed back

In this method, a fraction of output current is fedback to the input of the amplifier. It is also called current-shunt feedback circuit. Let  $A_i$  be the gain of the amplifier without feedback. If  $I_i$  is the input current, then the output current can be expressed as

$I_{out} = A_i \times I_i$ . Let a fraction  $m_i$  of the output current is fedback to the input through a resistance  $R_i$ .

Now, the feedback current  $I_f = m_i I_{out}$

Feedback fraction  $m_i = \frac{I_f}{I_{out}} = \frac{\text{feedback current}}{I_{out}}$

The negative current feedback reduces the input current to the amplifier and hence reduces the current gain

Fig. 3.3

#### 3.7 Negative feedback amplifier circuit

Consider the circuit shown in the fig. 3.4. There is change in emitter current following the input signal. This emitter current  $I_e$  produces a voltage drop  $I_e \times R_E$ . When emitter current

increases with increase in signal voltage, the base-emitter voltage decreases which gives the required negative feedback

The net input after negative feedback is

$$V_{BE} = V_s - i_e R_E = V_s - i_c R_E, \text{ sin } ce \ i_e = i_c$$

(3.7)

There is decrease in collector potential for increasing  $I_c$

Fig. 3.4

$$V_0 = -i_c R_c \quad \text{or} \quad i_c = -\frac{V_0}{R_c}$$

Substituting this value in eqn. (3.5),

$$V_{BE} = V_s + V_0 \frac{R_E}{R_c} = V_s + V_0 \beta \text{ since } \beta = R_E / R_c$$

Or  $\frac{V_{BE}}{V_0} = \frac{V_s}{V_0} + \beta$

*ie.*  $\frac{1}{A'} = \frac{1}{A} + \beta$

$\frac{1}{A'} = \frac{1 + A\beta}{A} \text{ or } A' = \frac{A}{1 + A\beta}$

When the gain A is large so that A $\beta$ >1

$$A' = \frac{A}{A\beta} = \frac{1}{\beta}$$

The closed loop gain of the negative feedback amplifier is

$A' = R_C / R_E$

Problem: An amplifier has a gain of 100 without feedback. If a negative feed back with feedback ratio of 0.1 is applied, find the new gain of the amplifier?

We know that, the gain of an amplifier with negative feedback is

$$A' = \frac{A}{1+A\beta}$$

. Here,  $A = 100$  and  $\beta = 0.1$

: Gain with feedback  $A' = \frac{A}{1+A\beta} = \frac{100}{1+(100\times0.1)} = \frac{100}{1+10} = \frac{100}{11} = 9.09$

So, the new gain with feedback= 9.09

An amplifier has a gain of 100 without feedback. When negative feedback is applied the gain is reduced to 50. Find the feedback fraction.

Given:  $A = 100; A' = 50; \beta = ?$

We know that the gain with negative feedback is  $A' = \frac{A}{1 + A\beta}$

$$A'(1 + A\beta) = A$$

le.  $A'A\beta = A - A'$

$\beta = \frac{A - A'}{AA'} = \frac{100 - 50}{100 \times 50} = 0.01$

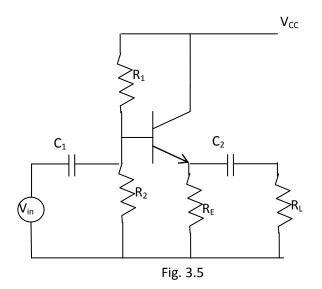

#### 3.8 Emitter Follower (Negative current feedback circuit)

The circuit shown in fig. 3.5 is the emitter follower circuit or common collector amplifier circuit. The ac voltage  $V_{in}$  is coupled into the base of the transistor through the coupling

Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli.

capacitor ( $C_1$ ). This ac signal rides on the DC base voltage or the Q point voltage. The ac signal appears at the emitter. This ac current signal produces a voltage across the emitter resistor  $R_E$ . The output is taken at the emitter by using coupling capacitor ( $C_2$ ).  $R_L$  is the load resistor.

The output voltage across the load resistor  $R_L$  is in phase with the input voltage. The output voltage follows the input voltage. The magnitude of the output voltage across the load resistor ( $R_L$ ) is approximately equal to the magnitude of the input voltage. This is the reason why this common collector amplifier is called emitter follower.

The emitter resistor  $R_E$  gives a negative feedback. This negative feedback causes many effects. First this negative feedback causes stability of the gain, second it reduces distortion and third it increases the input impedance. In any of the design in which these features are required, emitter follower circuit can be used. It provides low impedance at the output. Because of the feature of high impedance at the input and low impedance at the output, emitter follower circuit is used as pre-amplifier. One of the application example is the driving an audio speaker. The audio speaker has low impedance and for maximum power transfer into the speaker, the emitter follower is connected to the speaker. The voltage gain of the emitter follower circuit is approximately equal to unity. That is emitter follower circuit

Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli.

does not provide voltage gain. However it provides current gain and thereof power gain. Thus because of this current gain and power gain emitter follower is called an amplifier.

# 3.9 Oscillator

An electronic oscillator is a circuit that produces a periodic, oscillating electronic signal, often a sine wave or a square wave. Oscillators convert direct current (DC) from a power supply to an alternating current (AC) signal. They are widely used in many electronic devices. Common examples of signals generated by oscillators include signals broadcast by radio and television transmitters, clock signals that regulate computers and quartz clocks, and the sound produced by electronic beepers and video games.

Oscillators are characterized by the frequency generated at the output. They are,

- A low-frequency oscillator (LFO) is an electronic oscillator that generates a frequency below 20 Hz. This is used in the field of audio synthesizers, to distinguish it from an audio frequency oscillator.

- ii. An audio oscillator produces frequencies in the audio range, about 20 Hz to 20 KHz.

- iii. An RF oscillator produces signals in the radio frequency (RF) range of about 100 KHz to 100 GH

# 3.10 Essential requirements for an oscillator

- 1) **Amplifier**: which receives dc power from a dC source and convert it into ac power

- 2) **Tank circuit:** which consists of an inductor (L) and a capacitor (C) connected parallel to each other. The resonance frequency depends upon the values of L and C

- 3) **Feedback circuit**: A network providing a feedback of a fraction of the output back into the input. The feedback must be positive such that the feedback signal is in phase with the input signal.

# 3.11 Tank Circuit

A tank circuit or an oscillatory circuit is a parallel form of inductor and capacitor elements which produces the electrical oscillations of any desired frequency. Both these elements are capable of storing energy. Whenever the potential difference exists across a capacitor

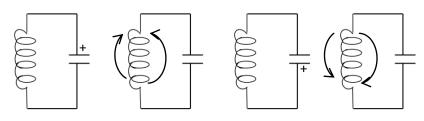

plates, it stores energy in its electric field. Similarly, whenever current flows thorough an inductor, energy is stored in its magnetic field. The figure 3.6 shows a tank circuit in which inductor L and capacitor C are connected in parallel.

FIG. 3.6

Let us consider that the capacitor is initially charged with a DC source having the polarities upper plate positive and lower plate negative as shown (fig. 3.6). This represents that the upper plate has of electrons deficiency , whereas the lower plate has excess of electrons. Therefore, potential differences exist between these two plates. Consider that this charged capacitor is connected across the inductor. The conventional current flow from positive polarity to negative polarity through the inductor coil. Therefore the energy stored or strength of the electric field in the capacitor decreases. The current flowing through the inductor induces an e.m.f. which opposes the electrons flow through it. This current flow set up a magnetic field around the inductor thereby it starts storing the magnetic energy. When the capacitor is fully discharged, current through the coil becomes zero. At this time magnetic field has maximum value and there is no electric field. Thus the electrical energy is converted into magnetic energy.

Once the capacitor is fully discharged, magnetic field around the inductor starts collapsing and produces the counter e.m.f. As per the Lenz's law, this counter e.m.f. produces the current which begin to charge the capacitor with opposite polarity by making plate upper plate negative and lower plate positive as shown in figure. When the capacitor is fully charged in opposite direction, the entire magnetic energy is converted back into the electric energy in capacitor, i.e., magnetic energy is collapsed. At this instant, capacitor starts discharging in the opposite direction. Once again the capacitor is fully discharged and this process will be continued. This continuous charging and discharging process results in an alternating motion of electrons which is nothing but an oscillating current.

## 3.12 Feedback oscillator

The most common form of linear oscillator is an electronic amplifier such as a transistor or operational amplifier connected in a feedback loop with its output fed back into its input through a frequency selective electronic filter to provide positive feedback. When the power supply to the amplifier is first switched on, electronic noise in the circuit provides a non-zero signal to get oscillations started. The noise travels around the loop and is amplified. Feedback oscillator circuits can be classified according to the type of frequency selective filter they use in the feedback loop.

In an *RC oscillator* circuit, the filter is a network of resistors and capacitors. RC oscillators are mostly used to generate lower frequencies, for example in the audio range. Common types of RC oscillator circuits are the phase shift oscillator and the Wien bridge oscillator.

In an *LC oscillator* circuit, the filter is a tuned circuit, called a *tank circuit* consisting of an inductor (L) and capacitor (C) connected parallel to each other. Charge flows back and forth between the capacitor's plates through the inductor, so the tuned circuit can store electrical energy oscillating at its resonant frequency. There are small losses in the tank circuit, but the amplifier compensates for those losses and supplies the power for the output signal. LC oscillators are often used at radio frequencies when a tunable frequency source is necessary, such as in signal generators, tunable radio transmitters and the local oscillators in radio receivers. Typical LC oscillator circuits are the Hartley, Colpitts and Clapp circuits

In a *crystal oscillator* circuit the filter is a piezoelectric crystal (commonly a quartz crystal). The crystal mechanically vibrates as a resonator, and its frequency of vibration determines the oscillation frequency. Crystals have very high Q-factor and also better temperature stability than tuned circuits, so crystal oscillators have much better frequency stability than LC or RC oscillators. Crystal oscillators are the most common type of linear oscillator, used to stabilize the frequency of most radio transmitters, and to generate the clock signal in computers and quartz clocks. Crystal oscillators often use the same circuits as LC oscillators, with the crystal replacing the tuned circuit. Quartz crystals are generally limited to frequencies of 30 MHz or below. Other types of resonator, dielectric resonators and surface

acoustic wave (SAW) devices, are used to control higher frequency oscillators, up into the microwave range. For example, SAW oscillators are used to generate the radio signal in cell phones.

#### 3.13 Colpitts Oscillator

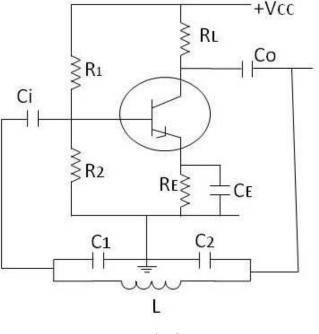

Colpitts oscillator was invented by American scientist Edwin Colpitts in 1918. It is another type of sinusoidal LC oscillator. In Colpitts oscillator the tank circuit consists of two capacitors in series and an inductor connected in parallel to the serial combination. The frequency of the oscillations are determined by the value of the capcitors and inductor in the tank circuit. In Colpitts oscillator, the capacitive voltage divider setup in the tank circuit works as the feed back source and this arrangement gives better frequency stability when compared to the Hartley oscillator which uses an inductive voltage divider arrangement for feedback. The circuit diagram of a typical Colpitts oscillator using transistor is shown in the fig. 3.7.

In the circuit diagram resistors  $R_1$  and  $R_2$  provide a voltage divider biasing to the transistor. Resistor  $R_C$  limits the collector current of the transistor.  $C_i$  is the input DC decoupling capacitor while  $C_o$  is the output decoupling capacitor.  $R_E$  is the emitter resistor and its meant for thermal stability.  $C_E$  is the emitter by-pass capacitor. The emitter by-pass capacitor is to by-pass the amplified AC signals from dropping across  $R_E$ . Capacitors  $C_1$ ,  $C_2$  and inductor L form the tank circuit. Feedback to the base of transistor is taken from the junction of Capacitor  $C_2$  and inductor L in the tank circuit.

When the power supply is switched ON, capacitors  $C_1$  and  $C_2$  start charging. When they are fully charged they start discharging through the inductor  $L_{-}$ . When the capacitors are fully discharged, the electrostatic energy stored in the capacitors get transferred to the inductor as magnetic flux. The inductor starts discharging and capacitors get charged again. This transfer of energy back and forth between capacitors and inductor is the basis of oscillation. Voltage across  $C_2$  is phase opposite to that of the voltage across the  $C_1$  and it is the voltage across  $C_2$  that is fed back to the transistor. The feedback signal at the base base of transistor appears in the amplified form across the collector and emitter of the transistor.

The energy lost in the tank circuit is compensated by the transistor and the oscillations are Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tiruneiveli.

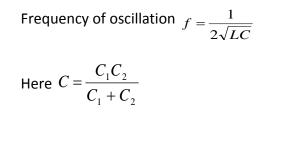

sustained. The tank circuit produces 180° phase shift and the transistor itself produces another 180° phase shift. That means the input and output are in phase and it is a necessary condition of positive feedback for maintaining sustained oscillations. The frequency of oscillations of the Colpitts oscillator is determined using the equation,

$$F = \frac{1}{2\pi\sqrt{LC}}$$

where L is the inductance value of the inductor in the tank circuit and C is the effective

Fig. 3.7

capacitance of the capacitors in the tank circuit. If  $C_1$  and  $C_2$  are the individual capacitance, then the effective capacitance of the serial combination  $C = C_1 C_2 / (C_1 + C_2)$ . By using variable capacitors in place of  $C_1$  and  $C_2$ , the frequency of Colpitts oscillator can be made variable.

ivianonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tiruneiveii.

## 3.14 Condition for oscillation

The condition for the functioning of the oscillator is  $A\beta > 1$ . In the given circuit, voltage gain  $A = R_c/r_e$ , where  $R_c$  is the load resistance and  $r_e$  is the dynamic resistance of base emitter junction.

So the condition for oscillation is

$$\frac{R_c}{r_e}\beta > 1$$

or

$$\frac{R_c}{r_e} > \frac{1}{\beta}$$

(3.7)

Feedback ratio  $\beta = \frac{\text{voltage fedback to the base}}{\text{output voltage}} = \frac{V_f}{V_0} = \frac{i/C_1\omega}{i/C_2\omega} = \frac{C_2}{C_1}$

Substituting in eqn. 3.7

$$\frac{R_c}{r_e} > \frac{C_1}{C_2}$$

Or  $h_{fe} > \frac{C_1}{C_2}$  where  $h_{fe} = \left(\frac{R_c}{r_c}\right)$  is called the forward current gain.

This is the condition for oscillation.

# 3.15 Expression for frequency

Resonance frequency is the oscillator frequency

At resonance,  $X_C = X_L$ . That is  $\frac{1}{C\omega} = L\omega$  where  $\frac{1}{C} = \frac{1}{C_1} + \frac{1}{C_2}$

Or

$$\omega^2 = \frac{1}{LC}$$

or  $\omega = 2\pi f = \frac{1}{LC}$

Or

$$f = \frac{1}{2\pi\sqrt{LC}}$$

This is the frequency of the colpitt's oscillator.

## 3.16 Advantages of Colpitts oscillator

Main advantage of Colpitts oscillator over Hartley oscillator is the improved performance in the high frequency region. This is because the capacitors provide a low reactance path for the high frequency signals and thus the output signals in the high frequency domain will be more sinusoidal. Due to the excellent performance in the high frequency region, the Colpitts oscillator can be even used in microwave applications. Collpitts oscillator is generally used in RF applications and the typical operating range is 20KHz to 300MHz.

In a Colpitts oscillator,  $C_1 = 0.01 \, \mu F$ ,  $C_2 = 0.001 \, \mu F$  and  $L = 100 \, mH$ . Find its frequency of operation?

Frequency of oscillation

$$f = \frac{1}{2\pi\sqrt{LC}}$$

.

Here the effective capacitance  $C = \frac{1}{C_1} + \frac{1}{C_2} = \frac{C_1C_2}{C_1 + C_2}$

*ie.*

$$C = \frac{0.01 \times 10^{-6} \times 0.001 \times 10^{-6}}{0.01 \times 10^{-6} + 0.001 \times 10^{-6}} = 0.0009 \times 10^{-6} \text{ F}$$

$$\therefore f = \frac{1}{2\pi\sqrt{LC}} = \frac{1}{2\times 3.14 \times \sqrt{100 \times 10^{-3} \times 9 \times 10^{-10}}} = 1.68 \times 10^4 \, Hz$$

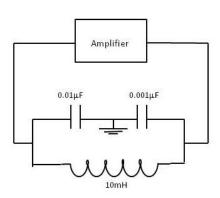

For the colpitt's oscillator circuit given in the fig. 3.8, find the operating frequency and feedback fraction

Manonmaniam Sundaranar University, Directorate of Distance & Cont

In our problem,

$$L = 10 \times 10^{-3} H$$

$$C_{1} = 0.001 \times 10^{-6} F \quad and \quad C_{2} = 0.01 \times 10^{-6} F$$

Fig. 3.8

$$\therefore C = \frac{0.01 \times 10^{-6} \times 0.001 \times 10^{-6}}{0.01 \times 10^{-6} + 0.001 \times 10^{-6}} = 0.0009 \times 10^{-6}$$

Hence, frequency of oscillation

$$f = \frac{1}{2 \times 3.14 \sqrt{10 \times 10^{-3} \times 0.0009 \times 10^{-6}}} = 53100 Hz$$

Fig. 3.8

Feedback fraction

$$\beta = \frac{C_1}{C_2} = \frac{0.001}{0.01} = \frac{1}{10}$$

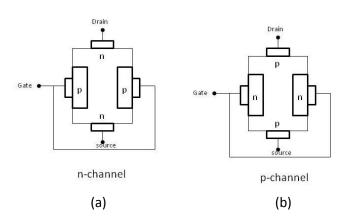

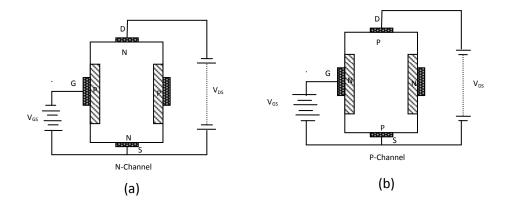

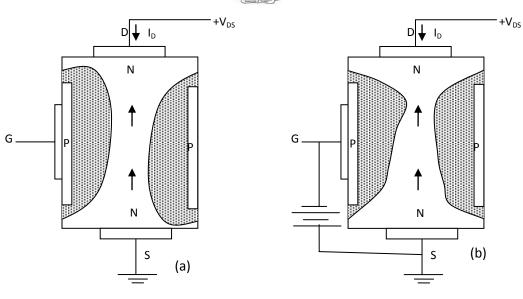

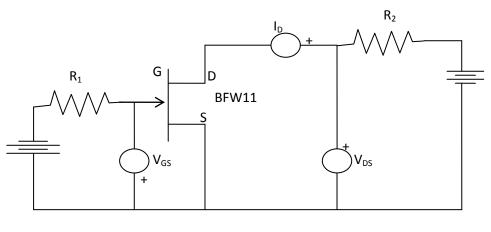

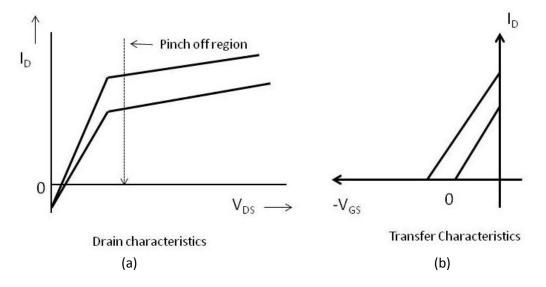

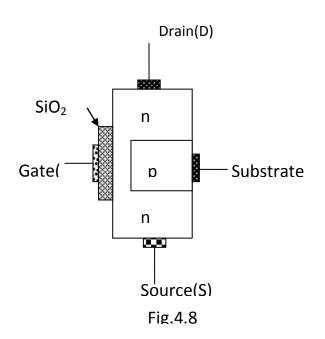

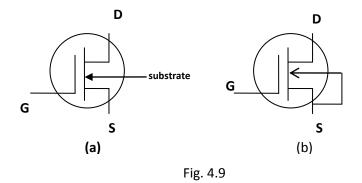

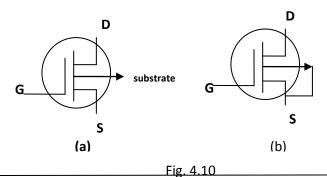

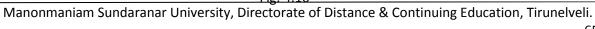

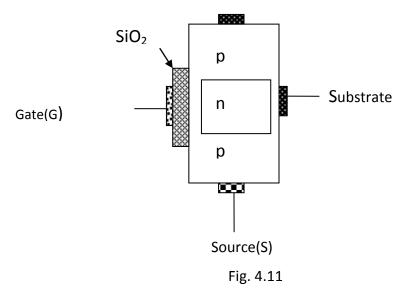

# **UNIT IV : FIELD EFFECT TRANSISTOR**

*Principle*, *features* and *characteristics* of *FET* – *JFET* and *MOSFET* – *their characteristics* – *enhancement* and *depletion* type

# 4.1 FIELD EFFECT TRANSISTOR

The field-effect transistor (FET) is a transistor that uses an electric field to control the flow of charges and hence the electrical conductivity of a channel of one type of charge carrier in a semiconductor material. There are two types of FET namely

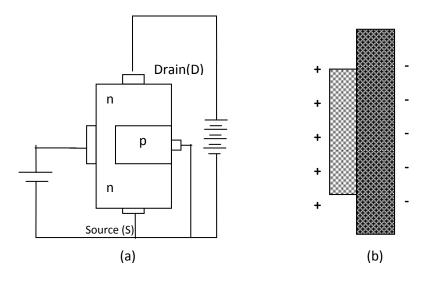

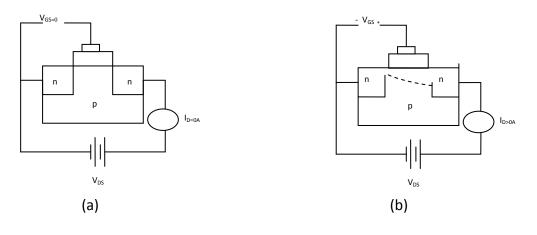

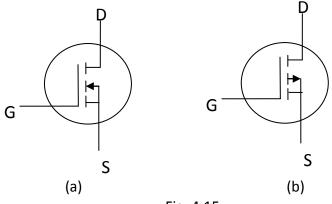

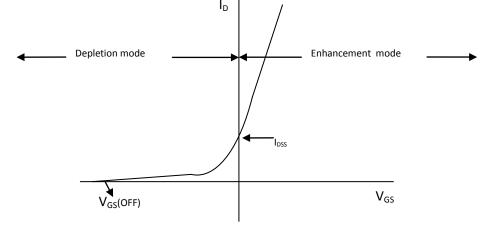

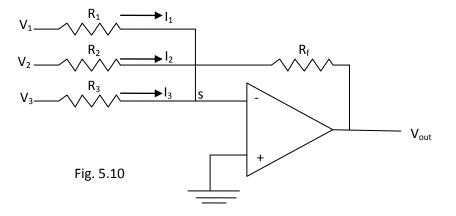

- 1. Junction Field Effect Transistor